#### Complete System PMIC, Featuring 13 Regulators, 8 GPIOs, RTC, and Flexible Power Sequencing for Multicore Applications

#### **General Description**

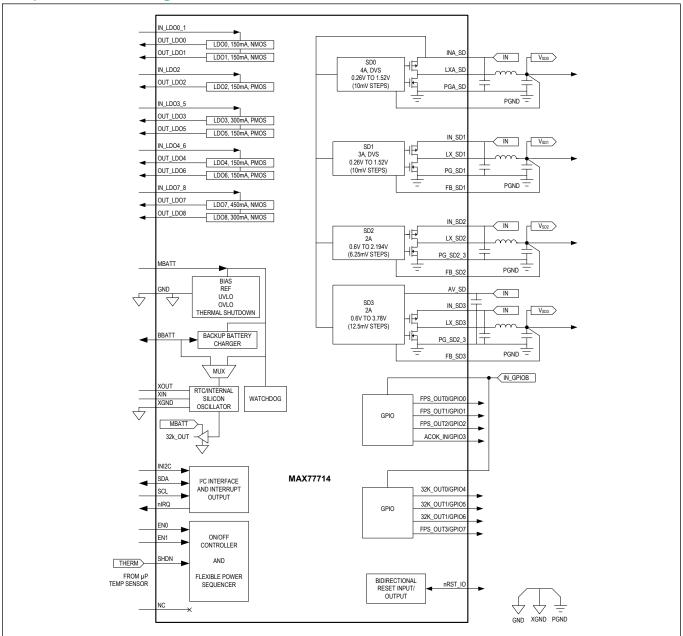

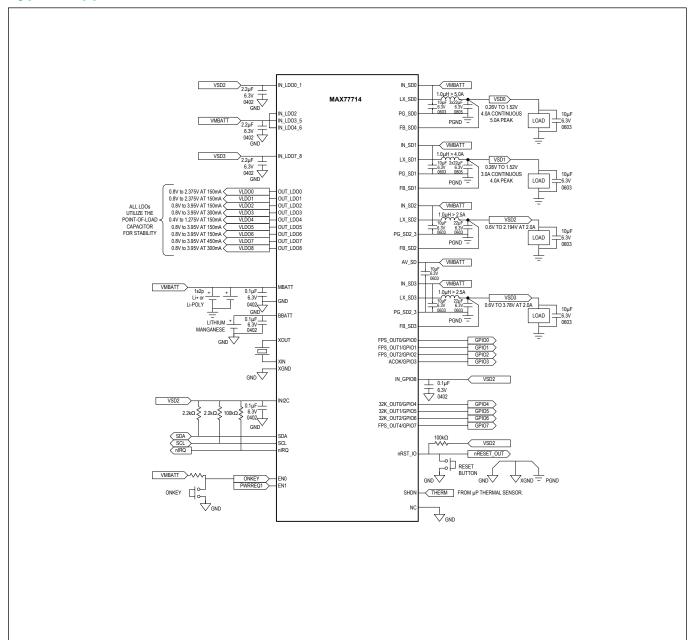

The MAX77714 is a complete power-management IC (PMIC) for portable devices using System-on-Chip (SoC) applications processors.

Two 2A (SD2/3), one 3A (SD1), and one 4A (SD0) step-down regulator switch at 2MHz, allowing the use of small magnetic components. The output voltages for SD0 and SD1 are programmable from 0.26V to 1.52V in 10mV steps. The output voltage for SD2 is programmable from 0.6V to 2.194V in 6.5mV steps. The output voltage for SD3 is programmable from 0.6V to 3.78V in 12.5mV steps.

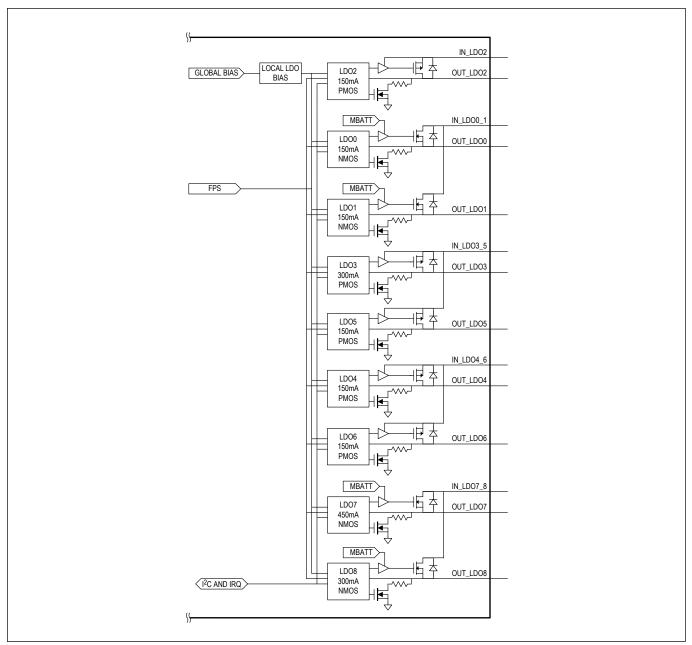

Nine low-dropout (LDO) linear regulators supply power to various system blocks. Each LDO features a programmable active-discharge circuit in shutdown. All LDOs feature two soft-start rates to limit inrush current during start up.

Eight programmable GPIOs can be programmed as general purpose inputs (GPI), general purpose outputs (GPO), or alternate modes for additional functionalities.

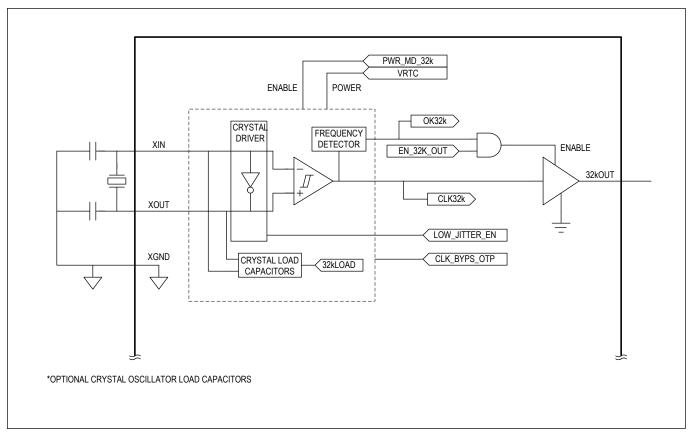

The real-time clock (RTC) with an external crystal oscillator provides time keeping and alarm wake-up functions. An internal silicon oscillator is available for systems that do not want to use the crystal oscillator. In addition, a watchdog timer is integrated for system monitoring purposes.

An integrated ON/OFF controller, in combination with flexible power sequencer (FPS), provides maximum flexibility in setting power-up/down sequences with minimal intervention from the applications processor.

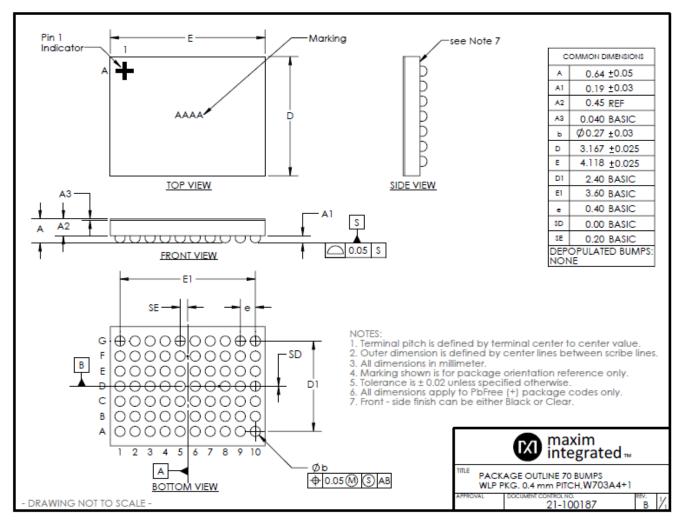

The 70-bump, 4.1mm x 3.25mm x 0.7mm, 0.4mm pitch wafer-level package (WLP) is ideal for space constrained applications.

Factory-programmable options allow the MAX77714 to be tailored for many applications. Contact the factory for more information about programmable options; minimum order quantities may apply.

#### **Applications**

- Drones

- Smartphones/Tablet PCs

- Handheld Gaming Devices

- AR/VR Headsets

- Streaming Devices/Set-Top Boxes

- Home Automation Hubs

- Digital Cameras

- Automotive Aftermarket Accessories

#### **Benefits and Features**

- Highly Integrated

- · 4x Buck Regulators

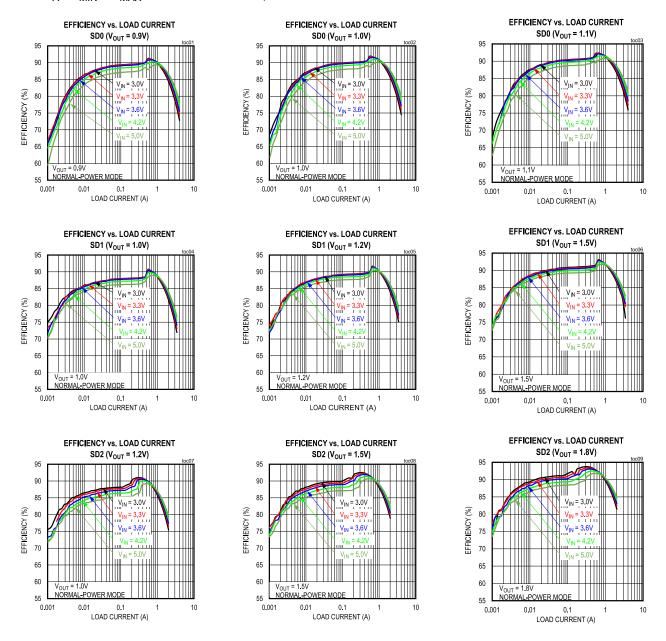

- SD0/1 Peak Efficiency >90% at 3.6V<sub>IN</sub> 1.1V<sub>OUT</sub>

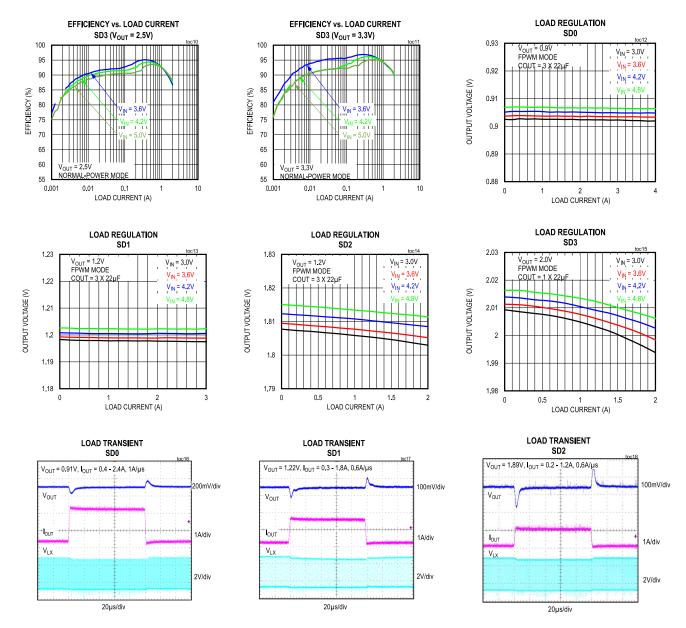

- SD2/3 Peak Efficiency >93% at 3.6V<sub>IN</sub> 1.8V<sub>OUT</sub>

- Supports LDDR4x Memory requirements

- · 9x Low-Dropout Linear Regulator

- Eight GPIOs

- Real-Time Clock

- · Backup Battery Charger

- · Bidirectional Reset I/O

- Interrupt Output

- · System Watchdog Timer

- Flexible and Configurable

- I<sup>2</sup>C-Compatible Interface

- · Factory OTP Options Available

- Flexible Power Sequencer

- Configurable Power-Up/Power-Down/Sleep Mode Entry/Exit Timing

- · Highly configurable GPIO ALT Modes

- Three Resources can be Configured as 32kHz Oscillator Output

- Four Resources can be Configured on FPS

- One Resource can be Configured as ACOK Input

- Low Power

- Low I<sub>O</sub> of 85µA in Sleep Mode

- SD0/1 Low-Power Quiescent Current is 10µA

- SD2/3 Low-Power Quiescent Current is 5µA

- LDO Low-Power Quiescent Current is 1.5µA

- Small Size

- 70-Bump, 0.4mm Pitch, 10x7 Ball Array WLP, 4.1mm x 3.25mm x 0.7mm Package Size

- 230mm<sup>2</sup> Total Solution Size

Ordering Information appears at end of data sheet.

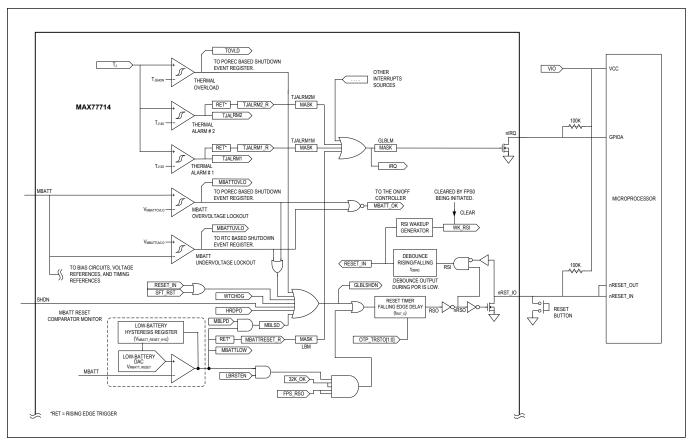

#### **Simplified Block Diagram**

#### **TABLE OF CONTENTS**

| General Description                                                 | . 1  |

|---------------------------------------------------------------------|------|

| Applications                                                        | . 1  |

| Benefits and Features                                               | . 1  |

| Simplified Block Diagram                                            | . 2  |

| Absolute Maximum Ratings                                            | 12   |

| Package Information                                                 | 12   |

| WLP                                                                 | 12   |

| Electrical Characteristics—Global Resources                         | 14   |

| Electrical Characteristics—ON/OFF Controller                        | 18   |

| Electrical Characteristics—Flexible Power Supply (FPS)              | 19   |

| Electrical Characteristics—Step-Down Regulators (SD0–4A Output)     | . 19 |

| Electrical Characteristics—Step-Down Regulators (SD1–3A Output)     | 21   |

| Electrical Characteristics—Step-Down Regulators (SD2/3–2A Output)   | 23   |

| Electrical Characteristics—150mA PMOS LDO (LDO2, LDO4, LDO5, LDO6)  | 25   |

| Electrical Characteristics—300mA PMOS LDO (LDO3)                    | 27   |

| Electrical Characteristics—150mA NMOS LDO (LDO0, LDO1)              | 29   |

| Electrical Characteristics—300mA NMOS LDO (LDO8)                    | 31   |

| Electrical Characteristics—450mA NMOS LDO (LDO7)                    | 32   |

| Electrical Characteristics—GPIO                                     | 34   |

| Electrical Characteristics—32kHz Oscillator                         | 35   |

| Electrical Characteristics—Backup Battery Charger                   | 36   |

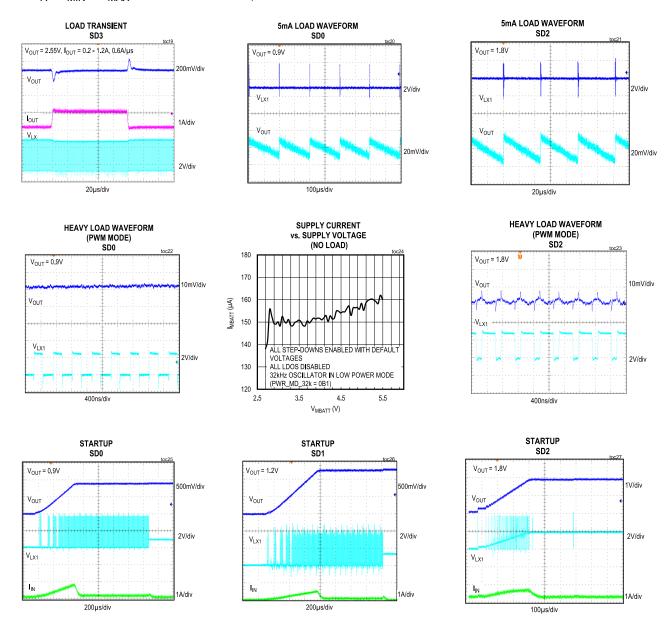

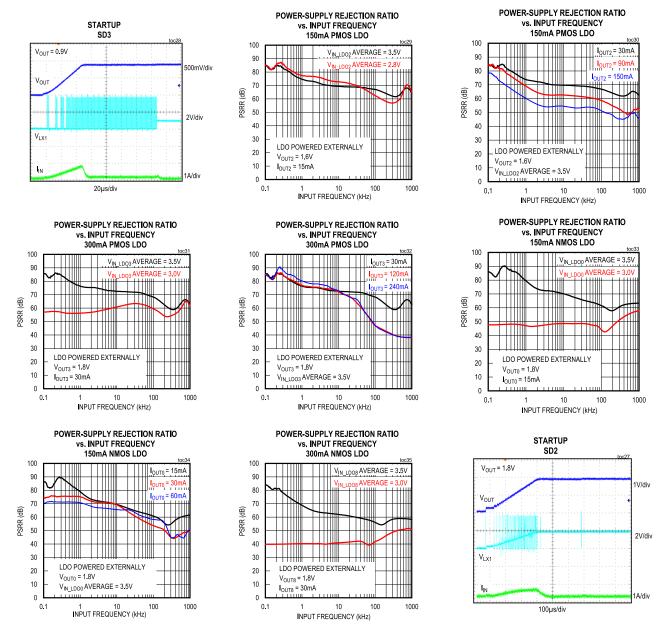

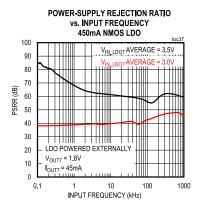

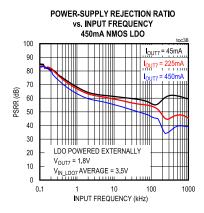

| Typical Operating Characteristics                                   | 37   |

| Bump Configuration                                                  | 42   |

| MAX77714                                                            | 42   |

| Bump Description                                                    | 42   |

| Detailed Description                                                | 46   |

| OTP Options                                                         | 46   |

| Detailed Description—Global Resources                               | 47   |

| Voltage References, Bias Currents, and Timing References            | 47   |

| Voltage Monitors                                                    | 47   |

| Thermal Monitors                                                    | 47   |

| Bidirectional Reset Input/Output                                    | 47   |

| Global Shutdown                                                     | 49   |

| Global Shutdown Events with Sequenced Shutdown and Automatic Wakeup | 49   |

| Global Shutdown Events with Sequenced Shutdown to the OFF State     | 49   |

| Global Shutdown Events with Immediate Shutdown                      | 50   |

| System Watchdog Timer                                               | 50   |

| TABLE OF CONTENTS (CONTINUED)                               |    |

|-------------------------------------------------------------|----|

| EN0 Functionality                                           | 51 |

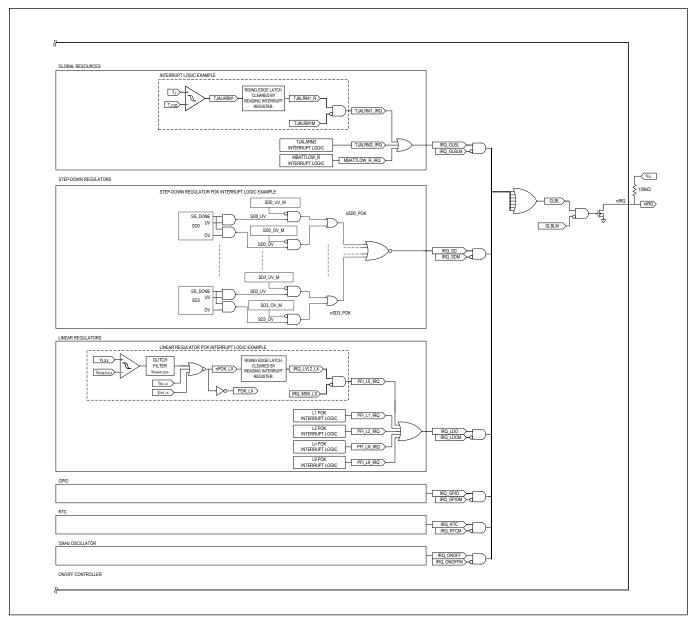

| Interrupt Logic                                             | 51 |

| Detailed Description—ON/OFF Controller                      | 52 |

| ON/OFF Controller                                           | 52 |

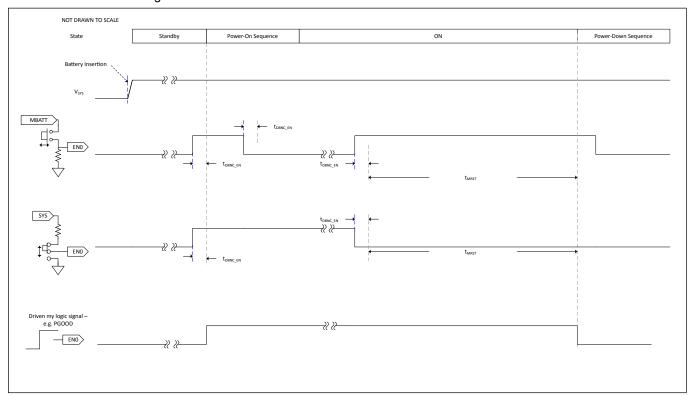

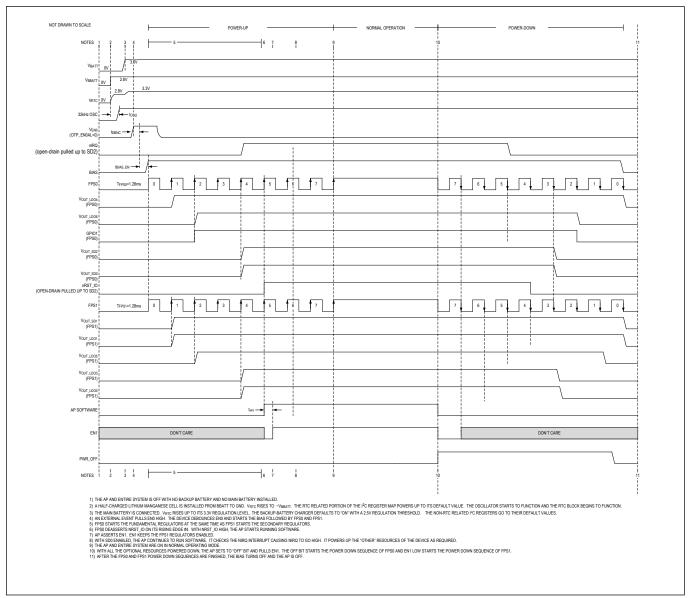

| Power-Up/Down Sequence                                      | 55 |

| Immediate Shutdown                                          | 57 |

| RESET                                                       | 58 |

| EN0                                                         | 58 |

| EN1                                                         | 58 |

| ACOK                                                        | 58 |

| SHDN                                                        | 58 |

| SMPL, ALARM1, and ALARM2                                    | 59 |

| MBATT_OK and MBATTLOW                                       | 59 |

| Resource Power Mode                                         | 59 |

| Detailed Description—Flexible Power Supply (FPS)            | 60 |

| Power-Off Event Recorder                                    | 60 |

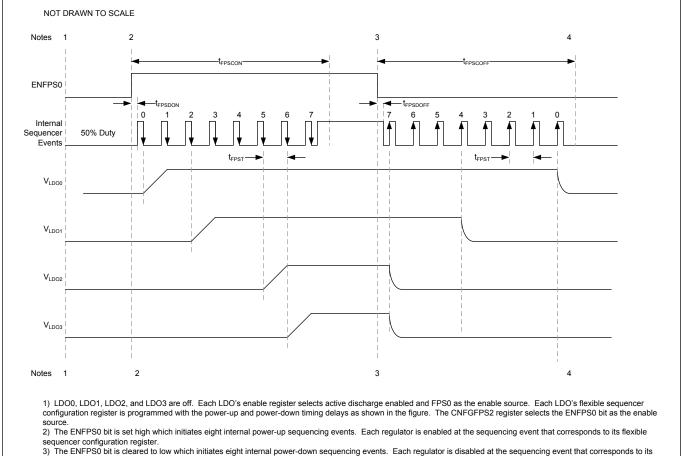

| Flexible Power Sequencer (FPS)                              | 60 |

| Features                                                    | 61 |

| FPS0                                                        | 61 |

| FPS1                                                        | 62 |

| FPS Sequence Power-Up/Down                                  | 62 |

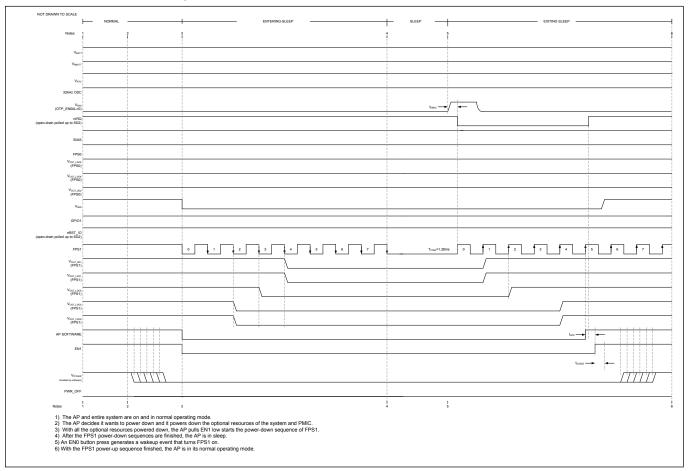

| FPS Sequence Sleep Entry/Exit                               | 63 |

| Detailed Description—Step-Down Regulators (SD0–4A Output)   | 63 |

| Active Discharge                                            | 63 |

| Output Monitoring                                           | 64 |

| Enable and Power Mode Control                               | 64 |

| PCB Layout Guidelines                                       | 65 |

| Detailed Description—Step-Down Regulators (SD1–3A Output)   | 65 |

| Active Discharge                                            | 65 |

| Output Monitoring                                           | 65 |

| Enable and Power Mode Control                               | 66 |

| Detailed Description—Step-Down Regulators (SD2/3–2A Output) | 66 |

#### TABLE OF CONTENTS (CONTINUED)

| _  |                                                  |    |

|----|--------------------------------------------------|----|

|    | Features and Benefits                            | 68 |

|    | Simplified Block Diagram                         | 69 |

|    | Active-Discharge Resistor                        | 70 |

|    | Input Capacitor Selection                        | 71 |

|    | Output Capacitor Selection                       | 71 |

|    | P-Channel Linear Regulator Output Capaciitor     | 71 |

|    | N-Channel Linear Regulator Output Capacitor      | 71 |

|    | Bias                                             | 72 |

|    | LDO Power Modes                                  | 72 |

|    | Soft-Start and Dynamic Voltage Scaling (DVS)     | 72 |

|    | Power-OK (POK) Comparators for Linear Regulators | 72 |

|    | Overvoltage Clamp                                | 73 |

| De | etailed Description—GPIO                         | 74 |

|    | GPIO                                             | 74 |

|    | Alternate Mode                                   | 74 |

|    | Features and Benefits                            | 74 |

|    | GPIO Programming Matrix                          | 75 |

| De | etailed Description—32kHz Oscillator             | 76 |

|    | Features: 32kHz Oscillator                       |    |

|    | Operation Modes                                  | 76 |

|    | Low-Jitter Mode and Low-Power Mode               | 77 |

|    | Internal Ballast Capacitors                      | 77 |

|    | Buffered Output.                                 | 78 |

|    | Silicon Oscillator                               | 78 |

| De | etailed Description—Backup Battery Charger       | 79 |

|    | Features                                         | 79 |

| De | etailed Description—Real-Time Clock (RTC)        | 80 |

|    | Features                                         | 80 |

|    | Writing to RTC                                   | 80 |

|    | Reading from RTC                                 | 81 |

|    | Sudden Momentary Power Loss (SMPL)               | 82 |

| De | etailed Description—I <sup>2</sup> C Interface   |    |

|    | I <sup>2</sup> C Slave Address                   | 82 |

| R  | egister Map                                      | 83 |

|    | RTC                                              |    |

|    | Register Details.                                | 84 |

|    | RTCINT (0x00)                                    | 84 |

|    | RTCINTM (0x01)                                   | 85 |

www.maximintegrated.com

#### TABLE OF CONTENTS (CONTINUED)

|   | RTCCNTLM (0x02)           | . 85 |

|---|---------------------------|------|

|   | RTCCNTL (0x03)            | . 86 |

|   | RTCUPDATE0 (0x04)         | . 87 |

|   | RTCUPDATE1 (0x05)         | . 88 |

|   | RTCSMPL (0x06)            | . 88 |

|   | RTCSEC (0x07)             | . 89 |

|   | RTCMIN (0x08)             | . 89 |

|   | RTCHOUR (0x09)            | . 89 |

|   | RTCDOW (0x0A)             | . 90 |

|   | RTCMONTH (0x0B)           | . 90 |

|   | RTCYEAR (0x0C)            | . 91 |

|   | RTCDOM (0x0D)             | . 91 |

|   | RTCSECA1 (0x0E)           | . 92 |

|   | RTCMINA1 (0x0F)           | . 92 |

|   | RTCHOURA1 (0x10)          | . 92 |

|   | RTCDOWA1 (0x11)           | . 93 |

|   | RTCMONTHA1 (0x12)         | . 94 |

|   | RTCYEARA1 (0x13)          | . 94 |

|   | RTCDOMA1 (0x14)           | . 94 |

|   | RTCSECA2 (0x15)           | . 95 |

|   | RTCMINA2 (0x16)           | . 95 |

|   | RTCHOURA2 (0x17)          | . 95 |

|   | RTCDOWA2 (0x18)           | . 96 |

|   | RTCMONTHA2 (0x19)         | . 97 |

|   | RTCYEARA2 (0x1A)          | . 97 |

|   | RTCDOMA2 (0x1B)           | . 97 |

|   | RTC_TIME_OK (0x25)        | . 98 |

| ı | PMIC-GPIO                 | . 98 |

| ı | Register Details          | 102  |

|   | INT_TOP (0x00)            | 102  |

|   | INT_MBATTRST_TEMP (0x01)  | 103  |

|   | INT_LVL2_ONOFF (0x02)     | 103  |

|   | INT_LVL2_SD0_3 (0x03)     | 104  |

|   | INT_LVL2_L0_7 (0x04)      | 105  |

|   | INT_LVL2_L8 (0x05)        | 106  |

|   | INT_LVL2_GPIO (0x06)      | 107  |

|   | INT_TOPM (0x07)           | 108  |

|   | INTM_MBATTRST_TEMP (0x08) | 109  |

www.maximintegrated.com

#### TABLE OF CONTENTS (CONTINUED)

| INTM_ONOFF (0x09)         | 109 |

|---------------------------|-----|

| INTM_SD0_3 (0x0A)         | 110 |

| INT_MSK_L0_7 (0x0B)       | 111 |

| INT_MSK_L8 (0x0C)         | 112 |

| STAT_MBATTRST_TEMP (0x0D) | 113 |

| STAT_ONOFF (0x0E)         | 113 |

| POERC0 (0x10)             | 114 |

| POERC1 (0x11)             | 115 |

| STAT_SD0_3 (0x20)         | 115 |

| 32K_STATUS (0x30)         | 116 |

| 32K_CONFIG (0x31)         | 116 |

| CNFG_GLBL1 (0x90)         | 117 |

| CNFG_GLBL2 (0x91)         | 118 |

| CNFG_GLBL3 (0x92)         | 118 |

| CNFG1_ONOFF (0x93)        | 119 |

| CNFG2_ONOFF (0x94)        | 120 |

| MSTR_PU_PD (0x95)         | 120 |

| MSTR_SLPENTRY_EXIT (0x96) | 121 |

| BUCK_PWR_MD (0x97)        | 121 |

| LDO_PWR_MD0_3 (0x98)      | 122 |

| LDO_PWR_MD4_7 (0x99)      | 124 |

| LDO_PWR_MD8 (0x9A)        | 125 |

| LDO0FPS (0x9B)            | 126 |

| LDO1FPS (0x9C)            | 127 |

| LDO2FPS (0x9D)            | 127 |

| LDO3FPS (0x9E)            | 128 |

| LDO4FPS (0x9F)            | 128 |

| LDO5FPS (0xA0)            | 129 |

| LDO6FPS (0xA1)            | 130 |

| LDO7FPS (0xA2)            | 130 |

| LDO8FPS (0xA3)            | 131 |

| SD0FPS (0xA4)             | 131 |

| SD1FPS (0xA5)             | 132 |

| SD2FPS (0xA6)             |     |

| SD3FPS (0xA7)             |     |

| GPIO0FPS (0xA8)           |     |

| GPIO1FPS (0xA9)           |     |

| GPIO2FPS (0xAA)           |     |

#### TABLE OF CONTENTS (CONTINUED)

| GPIO7FPS (0xAB)      | 135 |

|----------------------|-----|

| RSTIOFPS (0xAC)      | 136 |

| SD0_CNFG1 (0x40)     | 136 |

| SD1_CNFG1 (0x41)     | 137 |

| SD2_CNFG1 (0x42)     | 137 |

| SD3_CNFG1 (0x43)     | 137 |

| SD0_CNFG2 (0x44)     | 138 |

| SD0_CNFG3 (0x45)     | 139 |

| SD1_CNFG2 (0x46)     | 140 |

| SD1_CNFG3 (0x47)     | 141 |

| SD2_CNFG2 (0x48)     | 142 |

| SD2_CNFG3 (0x49)     | 142 |

| SD3_CNFG2 (0x4A)     | 143 |

| SD3_CNFG3 (0x4B)     | 144 |

| LDO_CNFG1_L0 (0x50)  | 145 |

| LDO_CNFG2_L0 (0x51)  | 145 |

| LDO_CNFG1_L1 (0x52)  | 146 |

| LDO_CNFG2_L1 (0x53)  | 146 |

| LDO_CNFG1_L2 (0x54). | 147 |

| LDO_CNFG2_L2 (0x55)  | 147 |

| LDO_CNFG1_L3 (0x56)  | 148 |

| LDO_CNFG2_L3 (0x57)  | 148 |

| LDO_CNFG1_L4 (0x58). | 149 |

| LDO_CNFG2_L4 (0x59)  | 149 |

| LDO_CNFG1_L5 (0x5A)  | 150 |

| LDO_CNFG2_L5 (0x5B)  | 150 |

| LDO_CNFG1_L6 (0x5C)  | 151 |

| LDO_CNFG2_L6 (0x5D)  | 151 |

| LDO_CNFG1_L7 (0x5E)  | 152 |

| LDO_CNFG2_L7 (0x5F)  | 152 |

| LDO_CNFG1_L8 (0x60)  | 153 |

| LDO_CNFG2_L8 (0x61)  | 153 |

| LDO_CNFG3 (0x62)     | 154 |

| CNFG_GPIO0 (0x70)    | 154 |

| CNFG_GPIO1 (0x71)    | 155 |

| CNFG_GPIO2 (0x72)    | 156 |

| CNFG_GPIO3 (0x73)    | 158 |

| CNFG_GPIO4 (0x74)    | 159 |

#### Complete System PMIC, Featuring 13 Regulators, 8 GPIOs, RTC, and Flexible Power Sequencing for Multicore Applications

|                   |   |      |      | •    |      |      |      |         |

|-------------------|---|------|------|------|------|------|------|---------|

| CNFG_GPIO5 (0x75) | ) | <br> | <br> | <br> | <br> | <br> | <br> | <br>160 |

| CNFG_GPIO6 (0x76) | ) | <br> | <br> | <br> | <br> | <br> | <br> | <br>161 |

| CNFG_GPIO7 (0x77) | ) | <br> | <br> | <br> | <br> | <br> | <br> | <br>162 |

| PUE_GPIO (0x78)   |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>164 |

| PDE_GPIO (0x79)   |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>165 |

| AME_GPIO (0x7A).  |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>166 |

| CID0 (0xB0)       |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>167 |

| CID1 (0xB1)       |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>167 |

| CID2 (0xB2)       |   | <br> | <br> | <br> | <br> | <br> | <br> | <br>168 |

TABLE OF CONTENTS (CONTINUED)

I2C CTRL2 (0xC1).....

### Complete System PMIC, Featuring 13 Regulators, 8 GPIOs, RTC, and Flexible Power Sequencing for Multicore Applications

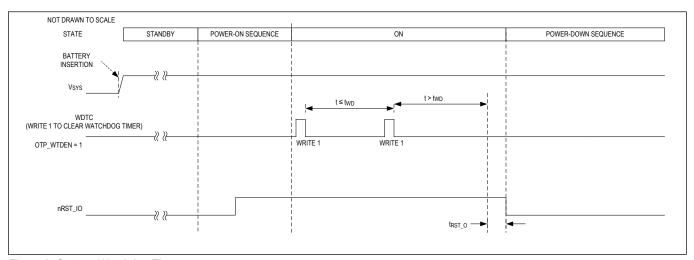

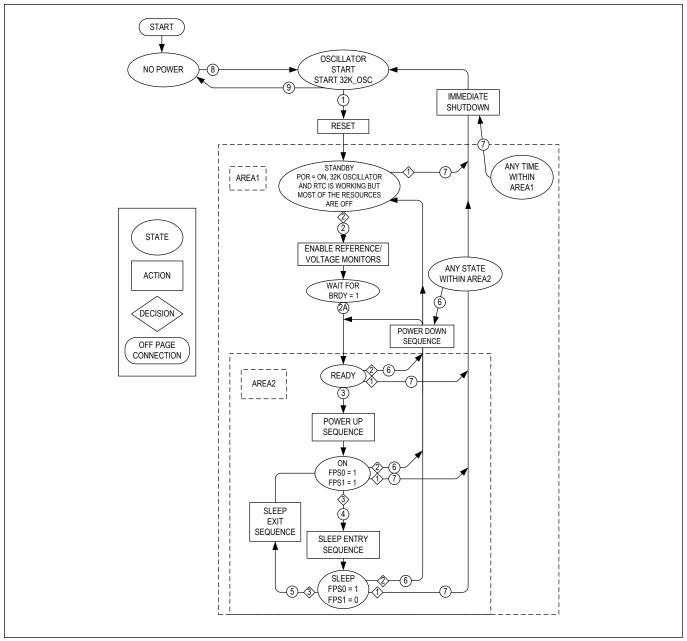

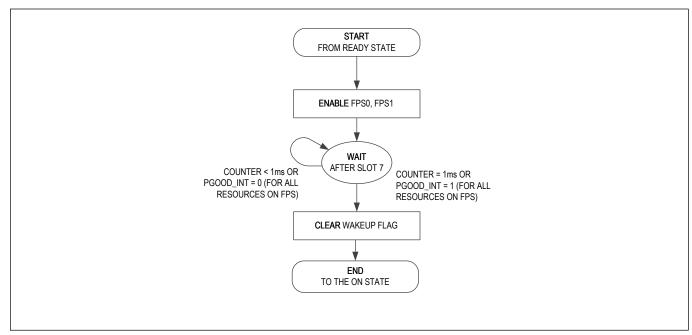

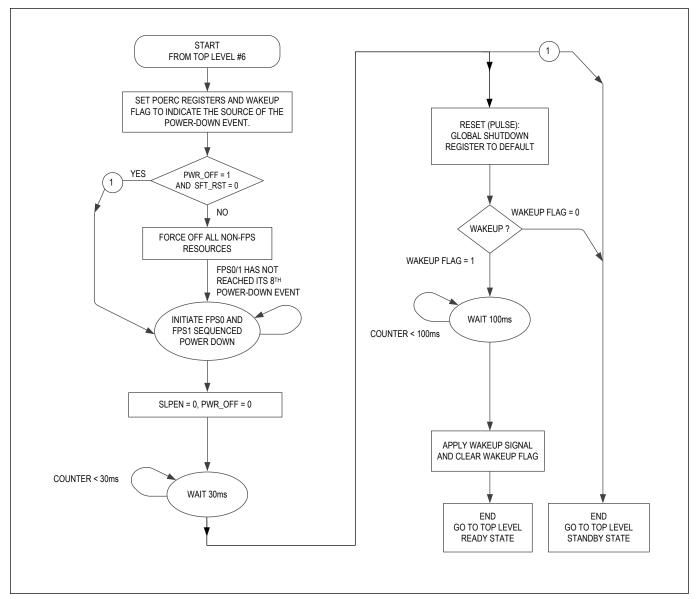

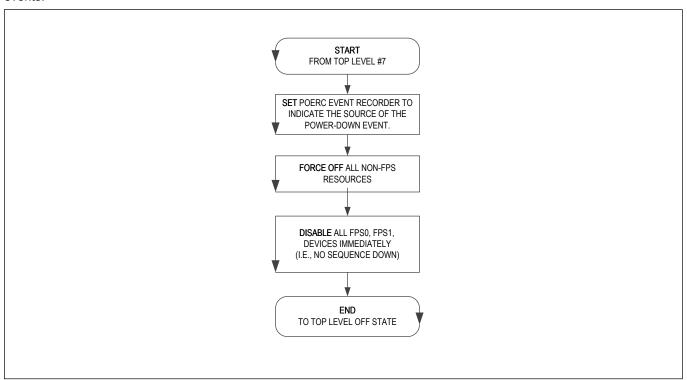

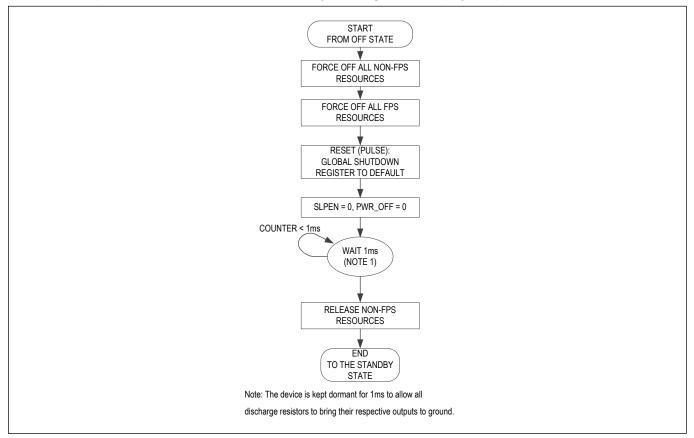

# Figure 1. Global Resource Logic. 48 Figure 2. System Watchdog Timer 50 Figure 3. EN0 Functionality Options 51 Figure 4. Simplified Interrupt Status and Mask Logic 52 Figure 5. State Diagram: ON/OFF Controller Top Level 53 Figure 6. Flow Chart—Power-Up Sequence 55 Figure 7. Flow Chart—Power-Down Sequence 56

www.maximintegrated.com Maxim Integrated | 10

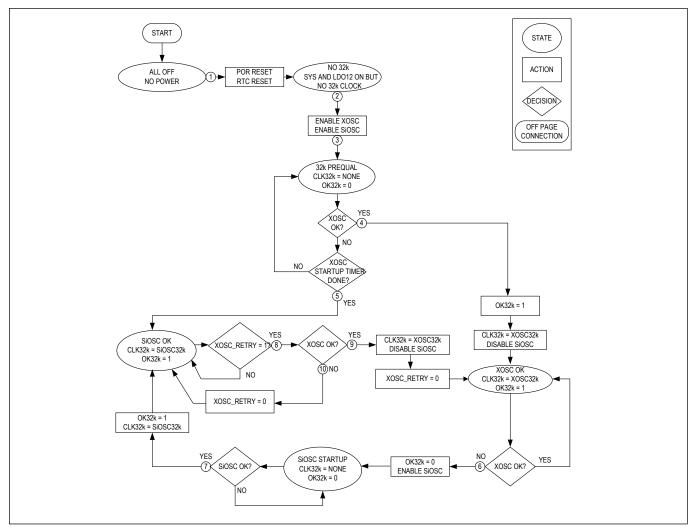

Figure 8. Flow Diagram: Immediate Shutdown57Figure 9. Reset Flow Diagram.58Figure 10. Flexible Power Sequencer.61Figure 11. FPS Sequence Power-Up/Down62Figure 12. FPS Sleep Entry/Exit63Figure 13. Linear Regulator Functional Diagram70Figure 14. Block Diagram—32kHz Normal-Mode Operation77Figure 15. Flow Chart—Silicon Oscillator79

# Complete System PMIC, Featuring 13 Regulators, 8 GPIOs, RTC, and Flexible Power Sequencing for Multicore Applications

| LIST OF TABLES                                     |    |

|----------------------------------------------------|----|

| Table 1. OTP Options                               | 46 |

| Table 2. ON/OFF Controller Transition Conditions   | 53 |

| Table 3. LDO and Step-Down Resource Power Mode     | 59 |

| Table 4. 32k Resource Power Mode                   | 59 |

| Table 5. Basic LDO Topologies                      | 69 |

| Table 6. GPIO Alternate Modes                      | 74 |

| Table 7. GPIO Programming Matrix                   | 75 |

| Table 8. 32kHz Crystal Oscillator Load Capacitance | 78 |

| Table 9. MAX77714 Slave Addresses                  | 82 |

#### **Absolute Maximum Ratings**

| Тор                  |                                                   | IN_SD0 to PG_SD0                   | 0.3V to +6.0V                                 |

|----------------------|---------------------------------------------------|------------------------------------|-----------------------------------------------|

| EN0 to GND           | 0.3V to V <sub>MBATT</sub> + 0.3V                 | IN_SD1 to PG_SD1                   | 0.3V to +6.0V                                 |

| EN1 to GND           | 0.3V to V <sub>MBATT</sub> + 0.3V                 | IN_SD2 to PG_SD2                   | 0.3V to +6.0V                                 |

| SHDN to GND          | 0.3V to V <sub>MBATT</sub> + 0.3V                 | LX_SD0 to PG_SD0 (Note 1)          |                                               |

| nRST_IO to GND       | 0.3V to V <sub>MBATT</sub> + 0.3V                 | LX_SD1 to PG_SD1 (Note 1)          | 0.3V to V <sub>IN</sub> <sub>SD1</sub> + 0.3V |

| nIRQ to GND          | 0.3V to V <sub>INI2C</sub> + 0.3V                 | LX_SD2 to PG_SD2 (Note 1)          |                                               |

| XOUT to XGND (Note1) | 0.3V to VRTC + 0.3V                               | LX_SDx RMS Current per Bump        | $(T_J = +110^{\circ}C)$ (RMS Current          |

| XIN to XGND (Note 1) | 0.3V to VRTC + 0.3V                               | per Pin (T <sub>J</sub> = +110°C)) | 1.6A                                          |

| BBATT to GND         | 0.3V to +6.0V                                     | FB_SD0/1 to GND                    | 0.3V to V <sub>MBATT</sub> + 0.3V             |

|                      | 0.3V to +6.0V                                     | PG_SDx to GND                      | 0.3V to +0.3V                                 |

| nRST_IO Sink Current | 20mA                                              | IN_SD3 to PG_SD3                   | 0.3V to +6.0V                                 |

| nIRQ Sink Current    | 20mA                                              | LX_SD3 to PG_SD3 (Note 1)          |                                               |

| DGND to GND          | 0.3V to +0.3V                                     | FB_SD2 to GND                      | 0.3V to V <sub>IN</sub> <sub>SD2</sub> + 0.3V |

| XGND to GND          | 0.3V to +0.3V                                     | FB_SD3 to GND                      | 0.3V to V <sub>IN</sub> <sub>SD3</sub> + 0.3V |

| LDO                  |                                                   | I <sup>2</sup> C                   | _                                             |

|                      | 0.3V to +6.0V                                     | SDA, SCL to GND                    | 0.3V to V <sub>INI2C</sub> + 0.3V             |

| OUT_LDO0 to GND      | 0.3V to V <sub>IN LDO0-1</sub> + 0.3V             | SDA Sink Current                   | 25mA                                          |

| IN_LDO2 to GND       | 0.3V to +6.0V                                     | GPIO                               |                                               |

| OUT_LDO1 to GND      | 0.3V to V <sub>IN LDO0-1</sub> + 0.3V             | GPIO_INB to GND                    |                                               |

| IN_LDO3_5 to GND     | 0.3V to +6.0V                                     | GPIO4-7 to GND                     | 0.3V to V <sub>GPIO INB</sub> + 0.3V          |

|                      | 0.3V to V <sub>IN LDO2</sub> + 0.3V               | GPIO0-3 to GND                     | 0.3V to V <sub>MBATT</sub> + 0.3V             |

|                      | 0.3V to +6.0V                                     | GPIOx Source Current               |                                               |

| OUT_LDO3 to GND      | 0.3V to V <sub>IN LDO3-5</sub> + 0.3V             | GPIOx Sink Current                 |                                               |

| IN_LDO7_8 to GND     | 0.3V to +6.0V                                     | Operating Temperature Range        | 40°C to +85°C                                 |

| OUT_LDO4 to GND      | 0.3V to V <sub>IN LDO4-6</sub> + 0.3V             | Junction Temperature               |                                               |

| OUT_LDO5 to GND      | 0.3V to $V_{IN}^{-}_{LDO3-5}$ + 0.3V              | Storage Temperature Range          | 40°C to +150°C                                |

| OUT_LDO6 to GND      | 0.3V to $V_{IN} L_{DO4-6} + 0.3V$                 | Soldering Temperature (reflow)     | +260°C                                        |

| OUT_LDO7 to GND      | 0.3V to V <sub>IN</sub> L <sub>DO7-8</sub> + 0.3V |                                    |                                               |

| OUT_LDO8 to GND      | 0.3V to V <sub>IN_LDO7-8</sub> + 0.3V             |                                    |                                               |

| Step-Down            | _                                                 |                                    |                                               |

Note 1: The specified voltage limitation is for steady state conditions. Dead times of a few nano seconds exist as the dynamic step-down regulator transitions from inductor charging to inductor discharging and vice versa. These dead times allow internal clamping diodes to PGNDx and INBx to forward bias (Vf~1V). When the LXx waveform is observed on a high-bandwidth oscilloscope (≥ 100MHz), the LXx transition edges are commonly seen with 1.5V spikes. These spikes are due to (1) the internal clamping diode forward voltage and (2) the high rate of current change through the current loop's inductance (V = L x di/dt). Designs must follow the recommended printed circuit board (PCB) layout in order to minimize this current loop's inductance.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **WLP**

| Package Code                           | W703A4+1                       |  |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|--|

| Outline Number                         | 21-100187                      |  |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                                |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 37.43°C/W                      |  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | NA                             |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics—Global Resources**

(Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range ( $T_A = -40$ °C to +85°C) and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                | SYMBOL                 | COND                                                                                                                                                                                                                                                                                                                                                                                      | ITIONS                                         | MIN | TYP | MAX  | UNITS |

|------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|------|-------|

| MAIN BATTERY POWER                       | R INPUT (MBATT         | )                                                                                                                                                                                                                                                                                                                                                                                         |                                                |     |     |      |       |

| MBATT Operating Voltage Range            | V <sub>MBATT</sub>     |                                                                                                                                                                                                                                                                                                                                                                                           |                                                | 2.6 |     | 5.5  | V     |

| MBATT Undervoltage-<br>Lockout Threshold | V <sub>MBATTUVLO</sub> | V <sub>MBATT</sub> falling, 200r                                                                                                                                                                                                                                                                                                                                                          |                                                | 2.5 |     | V    |       |

| MBATT Overvoltage<br>Lockout Threshold   | V <sub>MBATTOVLO</sub> | V <sub>MBATT</sub> rising, 200m                                                                                                                                                                                                                                                                                                                                                           | V <sub>MBATT</sub> rising, 200mV hysteresis    |     |     | 6.00 | V     |

|                                          | I <sub>Q_MBATT</sub>   | All regulators off, 32k<br>power mode (PWR_<br>V <sub>MBATT</sub> = 3.6V, I <sub>BBA</sub>                                                                                                                                                                                                                                                                                                | MD_32k = 0b1),                                 | 0.8 | 12  | 25   |       |

| Quiescent Supply<br>Current              | I <sub>Q_MBATT</sub>   | All regulators off, 32k<br>power mode (PWR_<br>internal reference an<br>(L_B_EN = 1), V <sub>MBA</sub><br>0µA                                                                                                                                                                                                                                                                             |                                                | 42  |     | μА   |       |

|                                          |                        | Current into MBATT and all LDO power inputs,                                                                                                                                                                                                                                                                                                                                              | Normal-power<br>mode, all LDOs<br>enabled      |     | 265 |      |       |

| No-Load LDO Supply<br>Current            |                        | V <sub>MBATT</sub> = 3.6V. All<br>LDO power inputs<br>are 3.6V, I <sub>BBATT</sub> =<br>0μA, LDOs set to<br>minimum output<br>voltage, all step-<br>down regulators<br>disabled, 32kHz<br>clock buffer<br>disabled, 32kHz<br>oscillator in low-<br>power mode<br>(PWR_MD_32k =<br>0b1),<br>V <sub>IN_GPIOB</sub> = 0V.<br>This does not<br>include any current<br>into nRST_IO or<br>nIRQ | Low-power mode,<br>LDO2-LDO6<br>enabled (PMOS) |     | 58  |      | μΑ    |

# Complete System PMIC, Featuring 13 Regulators, 8 GPIOs, RTC, and Flexible Power Sequencing for Multicore Applications

#### **Electrical Characteristics—Global Resources (continued)**

(Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range ( $T_A$  = -40°C to +85°C) and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                           | SYMBOL | COND                                                                                                                                                                                                                                                                                         | ITIONS                                                        | MIN | TYP  | MAX | UNITS |

|-------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|------|-----|-------|

|                                     |        | Current into MBATT and all step-down power inputs, V <sub>MBATT</sub> =                                                                                                                                                                                                                      | Normal-power<br>mode, all step-<br>down regulators<br>enabled |     | 145  |     |       |

| No-Load Step-Down<br>Supply Current |        | 3.6V, all regulator inputs are 3.6V, IBBATT = 0µA, all step-downs enabled with their minimum output voltages, all LDOs disabled, 32kHz clock buffer disabled, 32kHz oscillator in low-power mode (PWR_MD_32k = 0b01), VIN_GPIOB = 0V. This does not include any current into nRST_IO or nIRQ | Low-power mode,<br>all step-down<br>regulators enabled        |     | 82.5 |     | μΑ    |

#### **Electrical Characteristics—Global Resources (continued)**

(Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range ( $T_A$  = -40°C to +85°C) and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                    | SYMBOL | COND                                                                                                                                                                                                                                                                                                                                                                                 | ITIONS                                                           | MIN | TYP | MAX | UNITS |

|----------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| No-Load LDO and Step-<br>Down Supply Current |        | Current into MBATT all step- down power inputs, and all LDO power inputs, V <sub>MBATT</sub> = 3.6V, all regulator inputs are 3.6V, I <sub>BBATT</sub> = 0µA, all regulators set to minimum output voltage. 32kHz clock buffer disabled, 32kHz oscillator in low- power mode (PWR_MD_32k = 0b01), V <sub>IN_GPIOB</sub> = 0V. This does not include any current into nRST_IO or nIRQ | Normal-power<br>mode, all<br>regulators enabled                  |     | 375 | 520 | μΑ    |

|                                              |        | Current into MBATT all step- down power inputs, and all LDO power inputs, VMBATT = 3.6V, all regulator inputs are 3.6V, IBBATT = 0µA, all regulators set to minimum output voltage. 32kHz clock buffer disabled, 32kHz oscillator in low- power mode (PWR_MD_32k = 0b01), VIN_GPIOB = 0V. This does not include any current into nRST_IO or nIRQ                                     | Low-power mode,<br>all regulators<br>except LDO0/1/7/8<br>(NMOS) |     | 110 | 165 |       |

#### **Electrical Characteristics—Global Resources (continued)**

(Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range ( $T_A$  = -40°C to +85°C) and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                     | SYMBOL                   | CONDITIONS                                                                                        | MIN  | TYP   | MAX  | UNITS |

|-------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|------|-------|------|-------|

| MBATT RESET COMPA             | RATOR                    |                                                                                                   | •    |       |      | •     |

|                               |                          | MBATT_RESET[2:0] = 0b000                                                                          |      | 2.7   |      |       |

|                               |                          | MBATT_RESET[2:0] = 0b001                                                                          |      | 2.8   |      | 1     |

|                               |                          | MBATT_RESET[2:0] = 0b010                                                                          |      | 2.9   |      | 1     |

| Reset Falling Threshold       | V <sub>MBATT_RESE</sub>  | MBATT_RESET[2:0] = 0b011                                                                          | 2.95 | 3.0   | 3.05 | ] ,,  |

| Range                         | T                        | MBATT_RESET[2:0] = 0b100                                                                          |      | 3.1   |      | V     |

|                               |                          | MBATT_RESET[2:0] = 0b101                                                                          |      | 3.2   |      | 1     |

|                               |                          | MBATT_RESET[2:0] = 0b110                                                                          |      | 3.3   |      | 1     |

|                               |                          | MBATT_RESET[2:0] = 0b111                                                                          |      | 3.4   |      | 1     |

|                               |                          | MBATT_HYS[1:0] = b00                                                                              |      | 0.1   |      |       |

| Reset Threshold               | V <sub>MBATT_RES</sub>   | MBATT_HYS[1:0] = 0b01                                                                             |      | 0.2   |      | V     |

| Hysteresis                    | ET_HYS                   | MBATT_HYS[1:0] = 0b10                                                                             |      | 0.3   |      | ] V   |

|                               |                          | MBATT_HYS[1:0] = 0b11                                                                             |      | 0.4   |      | 1     |

| BIDIRECTIONAL RESET           | INPUT/OUTPUT             | (nRST_IO)                                                                                         | •    |       |      | 1     |

|                               |                          | OTP_TRSTO[1:0] = 0b00                                                                             | 0.8  | 1.0   | 1.2  | ms    |

| Reset Output Deassert         | _                        | OTP_TRSTO[1:0] = 0b01                                                                             |      | 8     |      |       |

| Delay Time                    | t <sub>RST_O</sub>       | OTP_TRSTO[1:0] = 0b10                                                                             |      | 32    |      |       |

|                               |                          | OTP_TRSTO[1:0] = 0b11                                                                             |      | 64    |      |       |

| Reset Input Debounce<br>Timer | t <sub>DBNC_nRST_I</sub> |                                                                                                   | 24   | 30    | 36   | ms    |

| Input High Voltage            | V <sub>IH</sub>          | RSO = 0                                                                                           | 1.4  |       |      | V     |

| Input Low Voltage             | V <sub>IL</sub>          | RSO = 0                                                                                           |      |       | 0.4  | V     |

| Input Hysteresis              | V <sub>HYS</sub>         | RSO = 0                                                                                           |      | 50    |      | mV    |

| January Community             |                          | V <sub>MBATT</sub> = 5.5V, V <sub>nRST_IO</sub> = 0V and<br>5.5V, RSO = 0, T <sub>A</sub> = +25°C |      | 0.001 | 1    |       |

| Input Leakage Current         |                          | V <sub>MBATT</sub> = 5.5V, V <sub>nRST_IO</sub> = 0V and 5.5V, RSO = 0, T <sub>A</sub> = +85°C    |      | 0.01  |      | μA    |

| Output Voltage Low            | V <sub>OL</sub>          | I <sub>SINK</sub> = 4mA, RSO = 1                                                                  |      |       | 0.4  | V     |

| Output High Leakage           |                          | V <sub>MBATT</sub> = 5.5V, V <sub>nRST_IO</sub> = 0V and<br>5.5V, RSO = 0, T <sub>A</sub> = +25°C |      | 0.001 | 1    |       |

| Current                       |                          | V <sub>MBATT</sub> = 5.5V, V <sub>nRST_IO</sub> = 0V and 5.5V, RSO = 0, T <sub>A</sub> = +85°C    |      | 0.01  |      | μA    |

| DEDICATED ACTIVE-LC           | W OPEN-DRAIN             | OUTPUTS (nIRQ)                                                                                    | •    |       |      | •     |

| Output Voltage Low            | V <sub>OL</sub>          | I <sub>SINK</sub> = 4mA, RSO = 1                                                                  |      |       | 0.4  | V     |

| Output High Leakage           |                          | V <sub>MBATT</sub> = 5.5V, V <sub>nIRQ</sub> = 0V and 5.5V,<br>RSO = 0, T <sub>A</sub> = +25°C    |      | 0.001 | 1    |       |

| Current                       | lozh                     | V <sub>MBATT</sub> = 5.5V, V <sub>nIRQ</sub> = 0V and 5.5V,<br>RSO = 0, T <sub>A</sub> = +85°C    |      | 0.01  |      | μA    |

#### **Electrical Characteristics—Global Resources (continued)**

(Limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range ( $T_A = -40$ °C to +85°C) and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                    | SYMBOL             | COND                                            | ITIONS                     | MIN | TYP | MAX | UNITS |  |  |

|------------------------------|--------------------|-------------------------------------------------|----------------------------|-----|-----|-----|-------|--|--|

| THERMAL ALARM & SHUTDOWN     |                    |                                                 |                            |     |     |     |       |  |  |

| Thermal Alarm 1              | T <sub>J110</sub>  | T <sub>J</sub> rising, +5°C hyste               | resis                      |     | 110 |     | °C    |  |  |

| Thermal Alarm 2              | T <sub>J130</sub>  | T <sub>J</sub> rising, +5°C hyste               |                            | 130 |     | °C  |       |  |  |

| Thermal Shutdown Temperature | T <sub>JSHDN</sub> | T <sub>J</sub> rising, +10°C hyst               |                            | 145 |     | °C  |       |  |  |

| BACKUP-BATTERY POV           | VER INPUT          |                                                 |                            |     |     |     |       |  |  |

| BBATT Current                | I <sub>BBATT</sub> | V <sub>MBATT</sub> = 0V,<br>PWR_MD_32k =<br>0b0 | V <sub>BBATT</sub> = 3.00V |     | 4.2 | 8   | μА    |  |  |

#### **Electrical Characteristics—ON/OFF Controller**

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER            | SYMBOL              | CONDITIONS       | MIN | TYP  | MAX | UNITS  |

|----------------------|---------------------|------------------|-----|------|-----|--------|

| ON/OFF CONTROLLER    |                     |                  |     |      |     | •      |

| Input Voltage High   | V <sub>IH</sub>     |                  | 1.4 |      |     | V      |

| Input Voltage Low    | V <sub>IL</sub>     |                  |     |      | 0.4 | V      |

| Input Hysteresis     | V <sub>HYS</sub>    |                  |     | 0.05 |     | V      |

|                      |                     | MRT[2:0] = 0b000 |     | 2    |     |        |

| Manual Reset Time    |                     | MRT[2:0] = 0b001 |     | 3    |     |        |

|                      |                     | MRT[2:0] = 0b010 |     | 4    |     |        |

|                      |                     | MRT[2:0] = 0b011 |     | 5    |     | ]      |

|                      | <sup>t</sup> HRDRST | MRT[2:0] = 0b100 |     | 6    |     | s<br>_ |

|                      |                     | MRT[2:0] = 0b101 |     | 8    |     |        |

|                      |                     | MRT[2:0] = 0b110 |     | 10   |     |        |

|                      |                     | MRT[2:0] = 0b111 |     | 12   |     |        |

|                      |                     | MRT[2:0] = 0b000 |     | 2    |     |        |

|                      |                     | MRT[2:0] = 0b001 |     | 2    |     | ]      |

|                      |                     | MRT[2:0] = 0b010 |     | 3    |     | 1      |

| Manual Reset Warning | _                   | MRT[2:0] = 0b011 |     | 4    |     | 1 .    |

| Time (MRWRN)         | t <sub>mrwrn</sub>  | MRT[2:0] = 0b100 |     | 5    |     | s      |

|                      |                     | MRT[2:0] = 0b101 |     | 6    |     | 1      |

|                      |                     | MRT[2:0] = 0b110 |     | 8    |     | 1      |

|                      |                     | MRT[2:0] = 0b111 |     | 10   |     | 1      |

#### **Electrical Characteristics—Flexible Power Supply (FPS)**

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                                  | SYMBOL           | CONDITIONS                                                           | MIN TY | P MAX | UNITS |

|------------------------------------------------------------|------------------|----------------------------------------------------------------------|--------|-------|-------|

| FLEXIBLE POWER SEQ                                         | UENCE            |                                                                      |        |       | •     |

| Flexible Power<br>Sequencer Enable<br>Delay                | tFSDON           | MAX77714 reference is already powered up prior to the enable command | 91     | .5    | μs    |

| Flexible Power<br>Sequencer Disable<br>Delay               | tFPSDOFF         |                                                                      | 15     | 2     | μs    |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b000                                   | 3      | 1     |       |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b001                                   | 63     | 3     | ]     |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b010                                   | 12     | 7     |       |

| Flexible Power                                             |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b011                                   | 25     | 6     | ]     |

| Sequencer Event Period                                     | t <sub>FST</sub> | MSTR_PU[2:0], MSTR_PD[2:0] = 0b100                                   | 50     | 8     | μs    |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b101                                   | 98     | 4     |       |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b110                                   | 193    | 36    | 1     |

|                                                            |                  | MSTR_PU[2:0], MSTR_PD[2:0] = 0b111                                   | 390    | 04    | 1     |

| Flexible Power<br>Sequencer Event Period<br>Timer Accuracy |                  | Accuracy of the flexible power sequencer clock                       | -15    | +15   | %     |

#### Electrical Characteristics—Step-Down Regulators (SD0-4A Output)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                          | SYMBOL                           | CONDITIONS                                                                                 | MIN  | TYP | MAX  | UNITS |

|----------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|------|-----|------|-------|

| SUPPLY VOLTAGE ANI                                 | CURRENT                          |                                                                                            |      |     |      | •     |

| Input Voltage Range                                | V <sub>INSD0</sub>               |                                                                                            | 2.6  |     | 5.5  | V     |

| OUTPUT VOLTAGE                                     |                                  |                                                                                            |      |     |      |       |

| Output Voltage Range                               | V <sub>OUT_SD0</sub>             | I <sup>2</sup> C programmable in 10mV steps<br>(SD0VOUT[6:0] = 0x01 to 0x7F)               | 0.26 |     | 1.52 | V     |

| Output Voltage<br>Accuracy                         | Vout_acc_n<br>M_sd0              | FPWM mode, normal-power mode, no load, T <sub>A</sub> = +25°C, V <sub>OUT_SD0</sub> = 1.0V | -2   |     | +2   | - %   |

|                                                    | V <sub>OUT_ACC_LP</sub><br>M_SD0 | Low-power mode, no load, T <sub>A</sub> = +25°C,<br>V <sub>OUT_SD0</sub> = 1.000V          | -4   |     | +4   | 76    |

| PERFORMANCE                                        |                                  |                                                                                            |      |     |      |       |

| Switching Frequency                                | f <sub>SW</sub>                  | V <sub>SYS</sub> = 3.6V                                                                    | 1.8  | 2   | 2.2  | MHz   |

| Line Regulation                                    |                                  | V <sub>INSD0</sub> = 2.6V to 5.5V, V <sub>OUT_SD0</sub> = 1.0V                             |      | 0.2 |      | %/V   |

| Coff Ctart Claw Data                               |                                  | SD0_SSRAMP = 0                                                                             |      | 2.5 |      | m)//a |

| Soft-Start Slew Rate                               |                                  | SD0_SSRAMP = 1                                                                             |      | 10  |      | mV/μs |

| Output Voltage Ramp-<br>Up/Down Slew Rate<br>(DVS) |                                  |                                                                                            |      | 10  |      | mV/μs |

#### Electrical Characteristics—Step-Down Regulators (SD0-4A Output) (continued)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                               | SYMBOL                  | CONDITIONS                                                               | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------|-------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| PMOS ON Resistance                                      | D                       | V <sub>SYS</sub> = V <sub>IN_SD0</sub> = 5V, I <sub>OUT</sub> = 150mA    |      | 38   | 60   | m0    |

| PINIOS ON RESISTANCE                                    | R <sub>ON_PCH</sub>     | V <sub>SYS</sub> = V <sub>IN_SD0</sub> = 3.6V, I <sub>OUT</sub> = 150mA  |      | 48   | 60   | mΩ    |

| NMOS ON Resistance                                      | B                       | V <sub>SYS</sub> = V <sub>IN_SD0</sub> = 5V, I <sub>OUT</sub> = 150mA    |      | 18   | 40   | mΩ    |

| NIVIOS ON RESISTANCE                                    | R <sub>ON_NCH</sub>     | V <sub>SYS</sub> = V <sub>IN_SD0</sub> = 3.6V, I <sub>OUT</sub> = 150mA  |      | 24   | 40   | 11122 |

| NMOS Zero-Crossing                                      | I <sub>ZX_SKIP</sub>    | SKIP mode                                                                |      | 20   |      | mA    |

| Threshold                                               | I <sub>ZX_PWM</sub>     | Low-power mode                                                           |      | 20   |      | IIIA  |

|                                                         | IL_LX_25C               | V <sub>LXSD0</sub> = 5.5V or 0V, T <sub>A</sub> = +25°C                  |      | 0.1  | 1    |       |

| LX Leakage                                              | I <sub>L_LX_85C</sub>   | $V_{LXSD0}$ = 5.5V or 0V, $T_A$ = +85°C (Note 2)                         |      | 1    |      | μA    |

| Output Active Discharge Resistance                      | R <sub>DISCHG_SD0</sub> | Resistance from FBB0 to PGND0, output disabled                           |      | 100  |      | Ω     |

| Turn-On Delay Time                                      | tON_DLY_SD0             | EN signal to LX switching with bias on                                   |      | 200  |      | μs    |

| OUTPUT CURRENT                                          |                         |                                                                          |      |      |      |       |

| Maximum Output<br>Current                               | IOUT_MAX_NM<br>_SD0     | RMS, normal mode                                                         | 4000 |      |      | mA    |

| PMOS Peak Current                                       |                         | T <sub>A</sub> = +25°C                                                   | 4825 | 5250 | 5675 | m^    |

| Limit                                                   | I <sub>LIMP</sub>       | T <sub>A</sub> = -40°C to +85°C                                          | 4825 | 5250 | 5675 | mA mA |

| NMOS Valley Current<br>Limit                            | I <sub>LIMV</sub>       |                                                                          |      | 3000 |      | mA    |

| NMOS (Negative)<br>Current Limit                        | I <sub>LIMN</sub>       |                                                                          |      | 2000 |      | mA    |

| BROWNOUT COMPARA                                        | TOR                     |                                                                          |      |      |      | •     |

|                                                         |                         | Normal-power mode, falling threshold, SD0_BO_THR[1:0] = 0b00             |      | 77   |      |       |

| Output-Brownout                                         |                         | Normal-power mode, falling threshold, SD0_BO_THR[1:0] = 0b01             | 81   |      |      |       |

| Threshold                                               | V <sub>BO_SD0</sub>     | Normal-power mode, falling threshold, SD0_BO_THR[1:0] = 0b10             |      | 85.7 |      | %     |

|                                                         |                         | Normal-power mode, falling threshold, SD0_BO_THR[1:0] = 0b11             |      | 91   |      |       |

| Output-Brownout<br>Accuracy                             |                         | Normal-Power Mode. V <sub>OUT_SD0</sub> = 1.0V (SD0_VOUT[6:0])           | -4.5 |      | +4.5 | %     |

| Output-Brownout<br>Threshold (Low-Power<br>Mode)        | V <sub>BO_SD0</sub>     | Falling threshold, low-power mode                                        |      | 86.0 |      | %     |

| Output-Brownout<br>Accuracy                             |                         | Low-power mode. V <sub>OUT_SD0</sub> = 1.0V<br>(SD0_VOUT[6:0])           | -4   |      | +4   | %     |

| Output-Brownout<br>Hysteresis Range                     | V <sub>BO_HYS_SD0</sub> | 2-Bit control over I <sup>2</sup> C. Max rising threshold limited to 96% | 5    |      | 20   | %     |

| Brownout-Voltage<br>Hysteresis Programming<br>Step Size |                         | Programmable with SD0_BO_HYS[1:0]                                        |      | 5    |      | %     |

#### Electrical Characteristics—Step-Down Regulators (SD0-4A Output) (continued)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                         | SYMBOL                  | CONDITIONS                  | MIN | TYP   | MAX | UNITS |

|---------------------------------------------------|-------------------------|-----------------------------|-----|-------|-----|-------|

| Output-Brownout<br>Hysteresis (Low-Power<br>Mode) | V <sub>BO_HYS_SD0</sub> |                             |     | 5     |     | %     |

| OV COMPARATOR                                     |                         |                             |     |       |     |       |

| Output OV Trip Level                              | V <sub>OUT_SD0_OV</sub> | Rising edge, SD0_OV_THR = 1 |     | 117.1 |     | %     |

| Output OV Hysteresis                              |                         | SD0_OV_THR = 1              |     | 8.6   |     | %     |

| Output OV Trip Level                              | V <sub>OUT_SD0_OV</sub> | Rising edge, SD0_OV_THR = 0 |     | 108.5 |     | %     |

| Output OV Hysteresis                              |                         | SD0_OV_THR = 0              |     | 3.9   |     | %     |

| Output OV Trip Level (Low-Power Mode)             | V <sub>OUT_SD0_OV</sub> | Rising edge, low-power mode |     | 108.3 |     | %     |

| Output OV Hysteresis (Low-Power Mode)             |                         | Low-power mode              |     | 3.9   |     | %     |

Note 2: Design guidance only and is not production tested.

#### Electrical Characteristics—Step-Down Regulators (SD1-3A Output)

$(V_{SYS} = 3.6V, T_A = -40$ °C to +85°C, limits are 100% tested at  $T_A = +25$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                  | SYMBOL                           | CONDITIONS                                                                           | MIN  | TYP | MAX  | UNITS |

|----------------------------|----------------------------------|--------------------------------------------------------------------------------------|------|-----|------|-------|

| SUPPLY VOLTAGE ANI         | CURRENT                          |                                                                                      |      |     |      | 1     |

| Input Voltage Range        | V <sub>IN_SD1</sub>              |                                                                                      | 2.6  |     | 5.5  | V     |

| OUTPUT VOLTAGE             |                                  |                                                                                      |      |     |      |       |

| Output Voltage Range       | V <sub>OUT_SD1</sub>             | I <sup>2</sup> C programmable in 10mV steps<br>(SD1VOUT[6:0] = 0x01 to 0x7F)         | 0.26 |     | 1.52 | V     |

| Output Voltage<br>Accuracy | Vout_ACC_N<br>M_SD1              | FPWM mode, normal mode, no load, T <sub>A</sub> = +25°C, V <sub>OUT_SD1</sub> = 1.0V | -2   |     | +2   | - %   |

|                            | V <sub>OUT_ACC_LP</sub><br>M_SD1 | Low-power mode, no load, T <sub>A</sub> = +25°C,<br>V <sub>OUT_SD1</sub> = 1.000V    | -4   |     | +4   | 70    |

| PERFORMANCE                |                                  |                                                                                      |      |     |      |       |

| Switching Frequency        | f <sub>SW</sub>                  | V <sub>MBATT</sub> = 3.6V                                                            | 1.8  | 2   | 2.2  | MHz   |

| Line Regulation            |                                  | V <sub>INSD1</sub> = 2.6V to 5.5V, V <sub>OUT_SD1</sub> = 1.0V                       |      | 0.2 |      | %/V   |

| PMOS ON Resistance         | Da.,                             | V <sub>MBATT</sub> = V <sub>INSD1</sub> = 5V, I <sub>OUT</sub> = 150mA               |      | 45  | 90   | mΩ    |

| FINOS ON Resistance        | R <sub>ON_PCH</sub>              | V <sub>MBATT</sub> = V <sub>INSD1</sub> = 3.6V, I <sub>OUT</sub> = 150mA             |      | 58  | 90   | 11122 |

| NMOS ON Resistance         | D                                | V <sub>MBATT</sub> = V <sub>INSD1</sub> = 5V, I <sub>OUT</sub> = 150mA               |      | 28  | 60   | mΩ    |

| INIVIOS ON Resistance      | R <sub>ON_NCH</sub>              | $V_{MBATT} = V_{INSD1} = 3.6V, I_{OUT} = 150mA$                                      |      | 35  | 60   | 11122 |

| NMOS Zero-Crossing         | I <sub>ZX_SKIP</sub>             | Skip mode                                                                            |      | 20  |      | m A   |

| Threshold                  | I <sub>ZX_PWM</sub>              | Low-power mode                                                                       |      | 20  |      | - mA  |

|                            | I <sub>L_LX_25C</sub>            | V <sub>LXSD1</sub> = 5.5V or 0V, T <sub>A</sub> = +25°C                              |      | 0.1 | 1    |       |

| LX Leakage                 | IL_LX_85C                        | V <sub>LXSD1</sub> = 5.5V or 0V, T <sub>A</sub> = +85°C (Note 3)                     |      | 1   |      | μA    |

#### Electrical Characteristics—Step-Down Regulators (SD1-3A Output) (continued)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                               | SYMBOL                  | CONDITIONS                                                               | MIN  | TYP   | MAX  | UNITS |

|---------------------------------------------------------|-------------------------|--------------------------------------------------------------------------|------|-------|------|-------|

| Output Active Discharge Resistance                      | R <sub>DISCHG_SD1</sub> | Resistance from FB_SD1 to PG_SD1, output disabled                        |      | 100   |      | Ω     |

| Turn-On Delay Time                                      | tON_DLY_SD1             | EN signal to LX switching with bias on                                   |      | 200   |      | μs    |

| BROWNOUT COMPARA                                        | TOR                     |                                                                          |      |       |      |       |

|                                                         |                         | Normal-power mode, falling threshold, SD1_BO_THR[1:0] = 0b00             |      | 77    |      |       |

| Output-Brownout                                         | V <sub>BO_SD1</sub>     | Normal-power mode, falling threshold, SD1_BO_THR[1:0] = 0b01             |      | 81    |      | %     |

| Threshold                                               |                         | Normal-power mode, falling threshold, SD1_BO_THR[1:0] = 0b10             |      | 85.7  |      |       |

|                                                         |                         | Normal-power mode, falling threshold, SD1_BO_THR[1:0] = 0b11             |      | 91    |      |       |

| Output-Brownout<br>Accuracy                             |                         | Normal-power mode. V <sub>OUT_SD1</sub> = 1.0V (SD1_VOUT[6:0])           | -4.5 |       | +4.5 | %     |

| Output-Brownout<br>Threshold (Low Power<br>Mode)        | V <sub>BO_SD1</sub>     | Falling threshold, low-power mode                                        |      | 86.0  |      | %     |

| Output-Brownout<br>Accuracy                             |                         | Low-power mode, V <sub>OUT_SD1</sub> = 1.0V (SD1_VOUT[6:0])              | -4   |       | +4   | %     |

| Output-Brownout<br>Hysteresis Range                     | V <sub>BO_HYS_SD1</sub> | 2-Bit control over I <sup>2</sup> C. Max rising threshold limited to 96% | 5    |       | 20   | %     |

| Brownout-Voltage<br>Hysteresis Programming<br>Step Size |                         | Programmable with SD1_BO_HYS[1:0]                                        |      | 5     |      | %     |

| Output-Brownout<br>Hysteresis (Low-Power<br>Mode)       | V <sub>BO_HYS_SDx</sub> |                                                                          |      | 5     |      | %     |

| OUTPUT CURRENT                                          |                         |                                                                          |      |       |      | •     |

| Maximum Output<br>Current                               | IOUT_MAX_NM<br>SD1      | RMS, normal mode                                                         | 3000 |       |      | mA    |

| PMOS Peak Current                                       |                         | T <sub>A</sub> = +25°C                                                   | 3825 | 4250  | 5100 | A     |

| Limit                                                   | I <sub>LIMP</sub>       | T <sub>A</sub> = -40°C to +85°C                                          | 3825 | 4250  | 5200 | - mA  |

| NMOS Valley Current<br>Limit                            | I <sub>LIMV</sub>       |                                                                          |      | 3000  |      | mA    |

| NMOS (Negative)<br>Current Limit                        | I <sub>LIMN</sub>       |                                                                          |      | 2000  |      | mA    |

| OV COMPARATOR                                           |                         |                                                                          | •    |       |      | •     |

| Output OV Trip Level                                    | V <sub>OUTSD1</sub> OV  | Rising edge, SD1_OV_THR = 1                                              |      | 117.1 |      | %     |

| Output OV Hysteresis                                    | _                       | SD1_OV_THR = 1                                                           |      | 8.6   |      | %     |

| Output OV Trip Level                                    | V <sub>OUTSD1_OV</sub>  | Rising edge, SD1_OV_THR = 0                                              |      | 108.5 |      | %     |

| Output OV Hysteresis                                    |                         | SD1_OV_THR = 0                                                           |      | 3.9   |      | %     |

#### Electrical Characteristics—Step-Down Regulators (SD1-3A Output) (continued)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                             | SYMBOL                 | CONDITIONS                  | MIN | TYP   | MAX | UNITS |

|---------------------------------------|------------------------|-----------------------------|-----|-------|-----|-------|

| Output OV Trip Level (Low-Power Mode) | V <sub>OUTSD1_OV</sub> | Rising edge, low-power mode |     | 108.3 |     | %     |

| Output OV hysteresis (Low-Power Mode) |                        | Low-power mode              |     | 3.9   |     | %     |

Note 3: Design guidance only and is not production tested.

#### Electrical Characteristics—Step-Down Regulators (SD2/3–2A Output)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range are guaranteed}$  by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                  | SYMBOL                            | CONDITIONS                                                         | MIN   | TYP  | MAX   | UNITS |

|----------------------------|-----------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

| SUPPLY VOLTAGE AND         | CURRENT                           |                                                                    | •     |      |       | •     |

| Input Voltage Range        | V <sub>IN_SDx</sub>               |                                                                    | 2.6   |      | 5.5   | V     |

| OUTPUT VOLTAGE             |                                   |                                                                    |       |      |       |       |

| Output Voltage Dance       | V <sub>OUT_SD2</sub>              | Programmable in 6.25mV steps with SD2VOUT[7:0]                     | 0.600 |      | 2.194 | V     |

| Output Voltage Range       | V <sub>OUT_SD3</sub>              | Programmable in 12.5mV steps with SD3VOUT[7:0]                     | 0.600 |      | 3.78  | V     |

|                            | V <sub>OUT_ACC_N</sub><br>M_SD2   | FPWM mode, normal-power mode, no load, V <sub>OUT_SD2</sub> = 1.1V | -2    |      | +2    |       |

| Output Voltage<br>Accuracy | VOUT_ACC_LP<br>M_SD2              | Low-power mode, no load, V <sub>OUT_SD2</sub> = 1.1V               | -4    |      | +4    | 0,    |

|                            | V <sub>OUT_ACC_N</sub><br>M_SD3   | FPWM mode, normal mode, no load, VOUT_SD3 = 1.1V                   | -2    |      | +2    | - %   |

|                            | VOUT_ACC_LP<br>M_SD3              | Low-power mode, no Load, V <sub>OUT_SD3</sub> = 1.1V               | -4    |      | +4    |       |

| OUTPUT CURRENT             |                                   |                                                                    | •     |      |       |       |

| Maximum Output<br>Current  | I <sub>OUT_MAX_NM</sub><br>_SD2_3 | RMS, normal mode, L = 1µH                                          | 2000  |      |       | mA    |

| PMOS Peak Current          | l=                                | V <sub>MBATT</sub> = 3.6V                                          | 2300  | 2875 | 4200  | - mA  |

| Limit                      | I <sub>LIMP</sub>                 | V <sub>MBATT</sub> = 5V                                            | 2300  | 2875 | 4200  | IIIA  |

| NMOS Valley Current        | li mari                           | V <sub>SYS</sub> = 3.6V                                            |       | 2125 |       | mA    |

| Limit                      | I <sub>LIMV</sub>                 | V <sub>SYS</sub> = 5V                                              |       | 2125 |       | IIIA  |

| NMOS Negative Current      | L                                 | V <sub>SYS</sub> = 3.6V                                            |       | 800  |       | mA    |

| Limit                      | I <sub>LIMN</sub>                 | V <sub>SYS</sub> = 5V                                              |       | 800  |       | IIIA  |

| PERFORMANCE                |                                   |                                                                    |       |      |       |       |

| Line Regulation            |                                   | V <sub>MBATT</sub> = V <sub>IN_SD2_3</sub> = 2.6V to 5.5V          |       | 0.2  |       | %/V   |

| Switching Frequency        | f                                 | V <sub>MBATT</sub> = 3.3V                                          | 1.8   | 2    | 2.2   | MU-   |

| Switching Frequency        | f <sub>SW</sub>                   | V <sub>MBATT</sub> = 5V                                            | 1.8   | 2    | 2.2   | MHz   |

| Coff Ctart Clay Data       |                                   | Fixed for SD2                                                      |       | 6.5  |       | mV/μs |

| Soft-Start Slew Rate       |                                   | Fixed for SD3                                                      |       | 17   |       |       |

#### Electrical Characteristics—Step-Down Regulators (SD2/3-2A Output) (continued)

$(V_{SYS} = 3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}C. \text{ Limits over the operating temperature range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                               | SYMBOL                  | CONDITIONS                                                                               | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Output Voltage Ramp-<br>Up Slew Rate                    |                         | Fixed for SD2, 3 (Notes 4, 7, 8 ), $C_{OUT}$ = $22\mu F$                                 |     | 40   |     | mV/μs |